寒假期间和几个小伙伴进行了交流,结果发现vivado的很多实用工具我都没有用上,导致连线和debug的时候很痛苦。。在这里分享一下~~

Vivado实用技巧

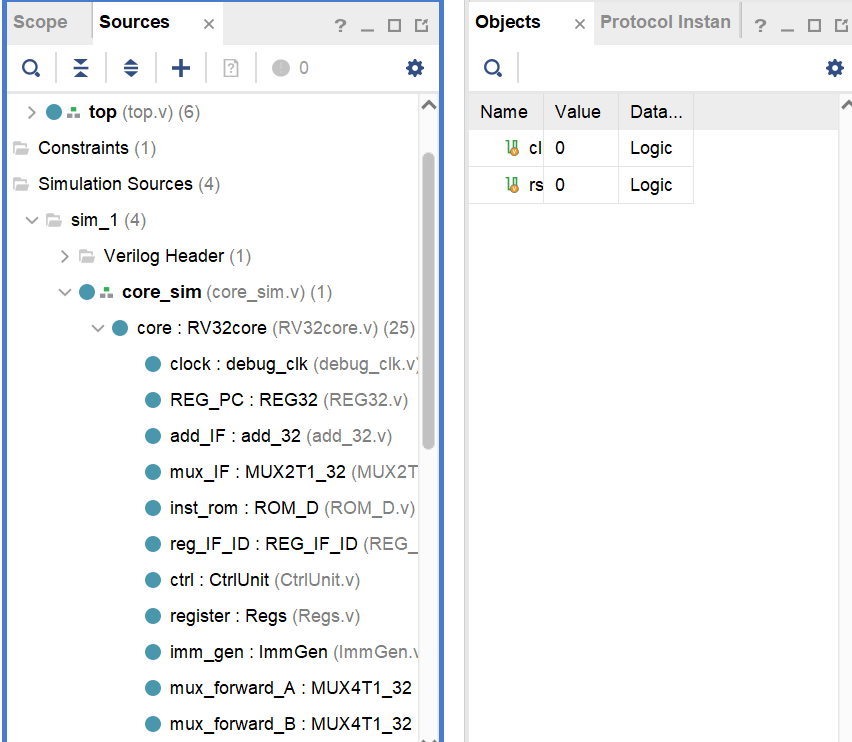

1) 仿真时查看子模块具体变量的值

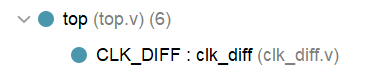

如图,假如说top被设置为仿真文件,如果子模块CLK_DIFF有一个reg变量a,那么在仿真过程中,我们是无法直接查看到a的值的。这对调试很不友好,那么有什么方法能看到其值呢?

答案:在仿真文件top中加入如下代码:

wire a1;

assign a1=CLK_DIFF.a;这样wire a1就能和子模块的a连了起来,接下来我们进行仿真,在仿真页面中。在左侧的source中找到object页面

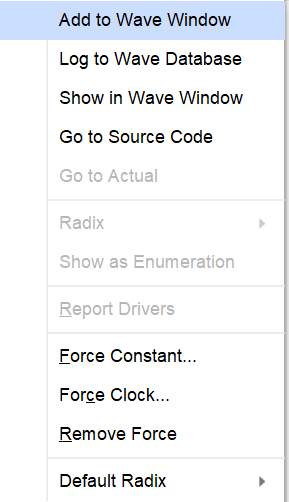

在 Object的搜索栏中搜索a1,右键,add to wave window

这样就可以在仿真图找到a1信号对应的值了

2)在编写verilog程序的时候,同一个变量不能在同一个时钟上沿(或下沿)的时候被改变两次;这样会导致multi-driven问题,导致无法生成比特流。

eg.

always @(posedge clk) begin

reg_a<=1'b1;

end

always @(posedge clk) begin

reg_a<=1'b0;

end

这样子虽然仿真不会报错,但显然会造成时序问题,使得生成的比特流无效

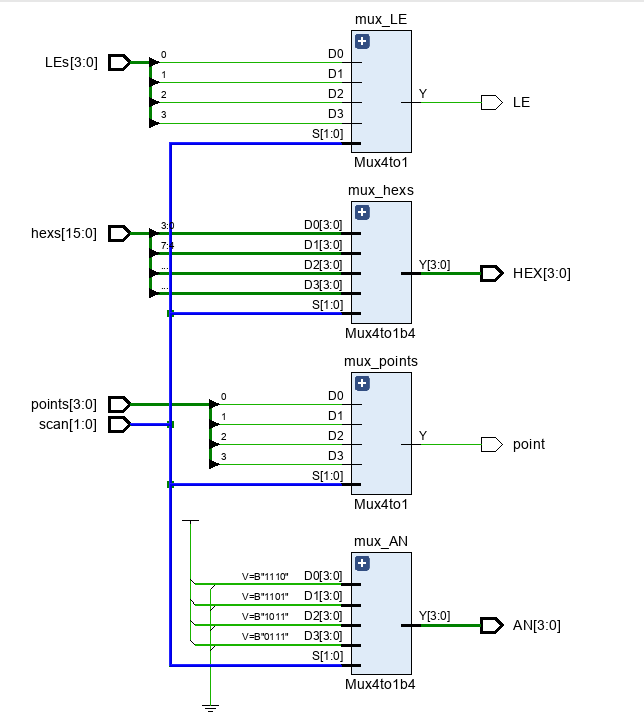

3) 通过schematic工具查看连线图

① 将要检查的模块设为top

② 打开schematic工具

③ 右侧显示连线图,可以单击某根线来查看此根线的所有连接情况

4) 复制工程的时候切记不能复制粘贴整个文件夹,这会导致副本和原工程共享同一个文件(即修改原工程的某个文件是时候,副本的这个文件也被修改了)

应该新建一个工程,然后创建文件,复制粘贴源码进去

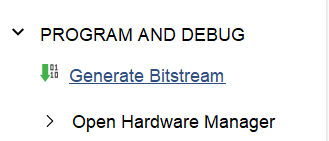

5) 对于需要反复调试的工程,可以把生成的比特流保存到其他位置;因为,一旦单击generate bitstream之后,不管有没有点击确认,上一次生成的比特流就会消失

资料

我们数字逻辑实验大程的报告(最后是优秀报告,被韬哥带飞)

计算机组成实验,仅供参考

crualcollegee/zju_computer_organization: zju 浙江大学 计组 计算机组成 实验 (包含所有bonus的正确代码)

暄暄学长的笔记写的很好,cache这部分完全没有听课,跟着他的笔记理清了这部分,,